【數字電路】鎖存器、觸發器電路分享-KIA MOS管

信息來源:本站 日期:2023-04-26

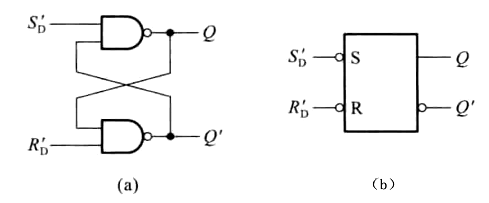

與非門R-S鎖存器

R-S鎖存器是靜態存儲單元中最基本的一種電路結構,通常由兩個或非門或者與非門組成,下圖為與非門搭建R-S鎖存器的電路結構圖。

基本RS鎖存器由電平觸發,并且有一個重要的約束條件:/SD和/RD不能同時為零。

即存在約束條件 RD ·SD=0

其中Q為初態,Q*為次態

電平觸發器

觸發器通常分為電平觸發,邊沿觸發,脈沖觸發

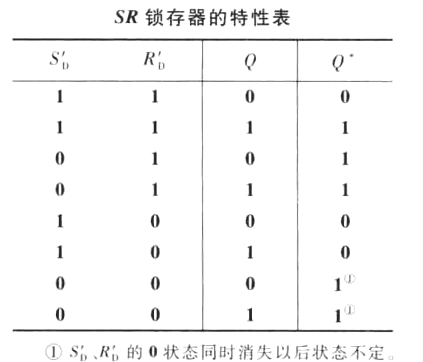

電平觸發RS鎖存器

由兩個與非門和SR鎖存器組成電平觸發器

只有當CLK=1為高電平時,G3、G4輸出端才收R和S輸入端控制

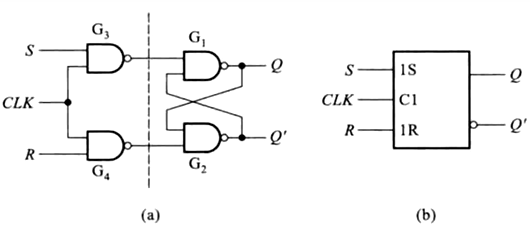

帶異步復位,異步置位的電平觸發RS鎖存器

只需在/SD和/RD加入低電平,即可將觸發器置1和置0;在正常由時鐘信號控制情況下/SD和/RD應為高電平。

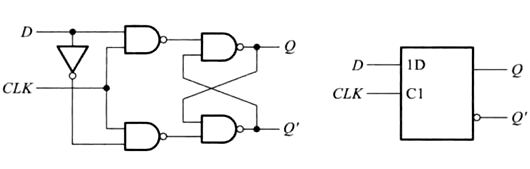

電平觸發D觸發器

電平觸發D觸發器,也稱D型鎖存器

若D為1,在CLK=1期間,輸出端Q為1,在CLK=0低電平期間,輸入端D無效,輸入端與非門置1,輸出端Q保持不變;若D為0,在CLK=1期間,輸出端Q為0,在CLK=0低電平期間,輸出端Q保持0不變,完成了鎖存功能。

邊沿觸發器

為提高觸發器可靠性,增強抗干擾能力,希望觸發器的次態僅僅取決于CLK信號上升沿或下降沿時刻輸入信號的狀態,而之前和之后的狀態不對輸出造成影響。

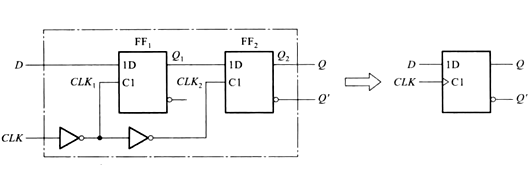

下圖為由兩個電平D觸發器搭建的邊沿觸發器

當CLK為低電平時,CLK1為高電平,FF1的輸出Q跟隨D變化而變化,保持Q1=D,此時CLK2為低電平,FF2的輸出Q2保持原來的狀態不變。

當CLK由低電平變高電平時,CLK1變為低電平,Q1保持為CLK上升沿到達前瞬間輸入端D的狀態(這也時setup存在的原因),此后不隨D的狀態而改變。而此時CLK2變為高電平,Q2跟隨當前時鐘沿傳輸的的數據Q1變化,此時Q被置位成時鐘上升沿瞬間D端的狀態,而于之后D的狀態無關。

聯系方式:鄒先生

聯系電話:0755-83888366-8022

手機:18123972950

QQ:2880195519

聯系地址:深圳市福田區金田路3037號金中環國際商務大廈2109

請搜微信公眾號:“KIA半導體”或掃一掃下圖“關注”官方微信公眾號

請“關注”官方微信公眾號:提供 MOS管 技術幫助

免責聲明:本網站部分文章或圖片來源其它出處,如有侵權,請聯系刪除。

<ul id="ou8ay"></ul>