nmos防反接保護(hù)電路,原理圖-KIA MOS管

信息來(lái)源:本站 日期:2024-08-23

基于NMOS的防反接電路如圖所示:

NMOS用于控制電源負(fù)極;

NMOS的漏極D接輸入電源負(fù)極,NMOS的源極S接板內(nèi)電源負(fù)極;

當(dāng)電源正接時(shí),上電初期,Vs=Vg=Vin,由于NMOS寄生二極管的存在,NMOS的漏極與源極導(dǎo)通,Vs=Vd+0.7V,而Vd=GND,故Vs=0.7V左右,Vgs=Vin-Vd6,選型合理的話,Vgs>Vth,故NMOS導(dǎo)通。導(dǎo)通后,設(shè)通過(guò)電流為I,NMOS的導(dǎo)通阻抗為Rds(on),則板內(nèi)地平面與輸入電源平面之間存在的壓降為△V=I*Rds(on)。故使用NMOS進(jìn)行防反接時(shí)需要關(guān)注由于導(dǎo)通阻抗帶來(lái)的回流問(wèn)題。

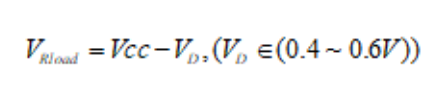

從圖中可以看出,電源電流走向先經(jīng)過(guò)負(fù)載然后從Q1 nmos的S極出nmos的D極,由于nmos的DS之間中存在寄生二極管,所以第一階段負(fù)載兩端的電壓為:

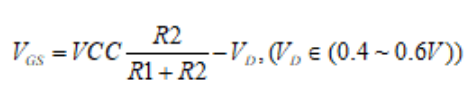

第二階段由于電源VCC還從R1、R2、Q1流過(guò),由于R1和R2的存在會(huì)在Q1 nmos的GS之間建立壓降:

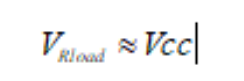

這是一個(gè)正反饋的原理,當(dāng)大于Q1 nmos的GS之間閾值電壓,那么Q1 nmos的DS之間就會(huì)被導(dǎo)通,隨著時(shí)間增加,nmos的DS之間就會(huì)等效為一個(gè)幾毫歐姆的電阻,就算在兩端流過(guò)大電流也不會(huì)有很大壓降產(chǎn)生。此時(shí)負(fù)載兩端電壓為:

通常在高電壓的場(chǎng)合,可以在R2兩端加一個(gè)穩(wěn)壓二極管,防止電源受到干擾產(chǎn)生尖峰波,從而使得nmos的GS之間電壓瞬間高于極限電壓Vgss而燒毀,從HY1603D的極限參數(shù)表中可以得到Vgss最高為20V。

當(dāng)然在低電壓的場(chǎng)合完全用不到穩(wěn)壓二極管D2,所以電路圖可以簡(jiǎn)化為下圖所示。

一般情況下nmos防反接電路

聯(lián)系方式:鄒先生

聯(lián)系電話:0755-83888366-8022

手機(jī):18123972950(微信同號(hào))

QQ:2880195519

聯(lián)系地址:深圳市福田區(qū)金田路3037號(hào)金中環(huán)國(guó)際商務(wù)大廈2109

請(qǐng)搜微信公眾號(hào):“KIA半導(dǎo)體”或掃一掃下圖“關(guān)注”官方微信公眾號(hào)

請(qǐng)“關(guān)注”官方微信公眾號(hào):提供 MOS管 技術(shù)幫助

免責(zé)聲明:本網(wǎng)站部分文章或圖片來(lái)源其它出處,如有侵權(quán),請(qǐng)聯(lián)系刪除。